Marking an industry first for emerging electronics devices, Semiconductor Research Corporation (SRC) today announced a significant expansion of its benchmarking research — a unique program that evaluates the relative capabilities of new and emerging computing devices.

SRC, the world’s leading university-research consortium for semiconductor technologies, is managing the initiative through its Nanoelectronics Research Initiative (SRC-NRI) and STARnet Research programs. The research will be led by the Georgia Institute of Technology’s Azad Naeemi, an associate professor in the School of Electrical and Computer Engineering (ECE).

Marking an industry first for emerging electronics devices, Semiconductor Research Corporation (SRC) today announced a significant expansion of its benchmarking research — a unique program that evaluates the relative capabilities of new and emerging computing devices.

SRC, the world’s leading university-research consortium for semiconductor technologies, is managing the initiative through its Nanoelectronics Research Initiative (SRC-NRI) and STARnet Research programs. The research will be led by the Georgia Institute of Technology’s Azad Naeemi, associate professor, Georgia Tech School of Electrical and Computer Engineering.

“Benchmarking guides university research funded through SRC — enabling concise communication of research outcomes, focusing researchers' attention on key technical challenges and sparking invention,” said Tom Theis, executive director of SRC-NRI. “Professor Naeemi's research is expected to take benchmarking of emerging devices to a new level of sophistication.”

Evaluating the performance of devices in representative "benchmark" circuits is a well-established engineering practice in the semiconductor industry. However, this new program is the first to develop a comparable methodology for evaluating the relative capabilities of emerging devices.

These emerging devices include, for example, transistor-like “steep slope” devices that can operate at very low voltage and, therefore, very low power, and non-volatile magnetic devices that combine the functions of logic and memory. The new devices operate by a variety of principles fundamentally different from those governing the operation of established silicon field-effect transistor technology.

In recent years, benchmarking of these devices has steadily increased in rigor. The Georgia Tech team — selected by a group of SRC member companies supporting the initiative including IBM, Intel Corporation, Micron Technology and Texas Instruments — will build on this foundation.

“This research will also enable selection of the most promising emerging devices for technology transfer to SRC member companies and for continued development in future SRC research programs,” said Gilroy Vandentop, executive director of STARnet Research.

Besides maintaining and improving the established benchmarking methodology, the Georgia Tech team is tasked with developing and evaluating benchmark circuits to better understand the potential of new devices for memory arrays, to explore and quantify the value of non-volatility and to measure the impact of various ways of implementing device-to-device connections. Perhaps most challenging, Naeemi will lead the development of a rigorous benchmarking methodology for non-Boolean (analog) computational circuits being explored for future applications such as artificial neural networks.

“Our team is chartered with maintaining and improving the established benchmarking methodology for emerging devices, evaluating the potential performance of the various SRC-NRI and STARnet devices in the established benchmark circuits,” said Naeemi. “We will incorporate additional device concepts as they emerge through ongoing research, and we will develop additional benchmark circuits to better understand the capabilities of these devices.”

The SRC benchmark program is a two-and-a-half year effort that funds research from July 1, 2015 through the close of 2017. For more information on the program, visit https://www.src.org/program/nri/benchmarking/.

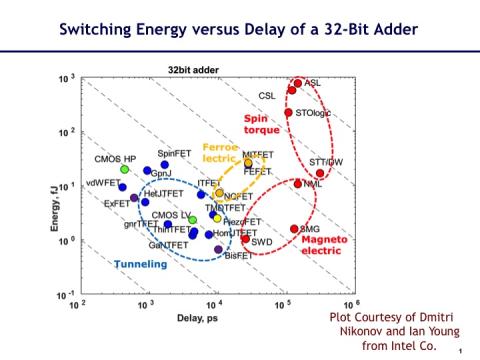

Caption for Switching Energy versus Delay of a 32-Bit Adder: Benchmarking results: Assessment of energy versus delay of a 32-bit adder circuit if it were built with various devices being explored in the Semiconductor Research Corporation's NRI and STARnet programs (Source: Dimitri Nikonov and Ian Young from Intel Co.).

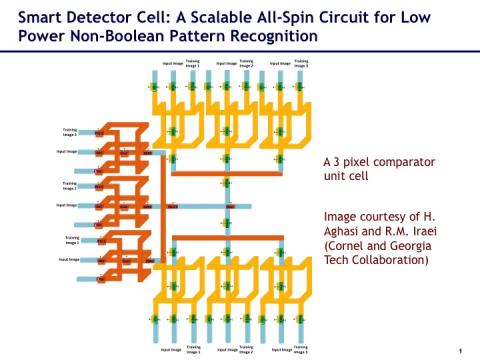

Caption for Smart Detector Cell: This circuit built from spintronic devices is being studied for possible addition to the established suite of SRC benchmark circuits (Source: H. Aghasi and R.M. Iraei from Cornell University and Georgia Tech).

Additional Images