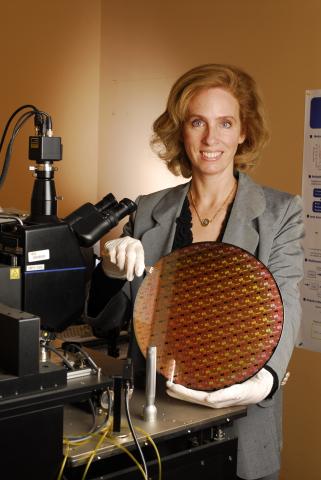

ECE Professor Linda S. Milor and her students – T. Liu, C.-C. Chen, and S. Cha – received the Best Paper Award at ESREF 2015 (European Symposium on Reliability of Electron Devices, Failure Physics, and Analysis), held October 5-9 in Toulouse, France.

Linda S. Milor and her students – T. Liu, C.-C. Chen, and S. Cha – received the Best Paper Award at ESREF 2015 (European Symposium on Reliability of Electron Devices, Failure Physics, and Analysis), held October 5-9 in Toulouse, France. Milor is a professor in the Georgia Tech School of Electrical and Computer Engineering (ECE) and leads the Yield Enhancement and Testing Research Group.

The title of the award-winning paper is “System-level variation-aware aging simulator using a unified novel gate-delay model for bias temperature instability, hot carrier injection, and gate oxide breakdown,” and it was published in Microelectronics and Reliability, vol. 55, nos. 9-10, pp. 1334-1340, August-September 2015.

The paper presents software that has been developed to estimate the lifetime of logic circuits due to a variety of front-end-of-line (FEOL) wearout mechanisms. It takes into account operating temperatures, IR drops, and stress probabilities while running benchmarks. It also takes into account system performance requirements, several FEOL wearout mechanisms (gate oxide breakdown, hot carrier injection, bias temperature instability), and a wide variety of use scenarios. Statistical analysis identifies critical paths and provides accurate estimates of the distribution of lifetimes under process, supply voltage, temperature, and aging variations. The software enables the replacement of arbitrary timing guardbands for aging with guardbands based on process data and system usage.