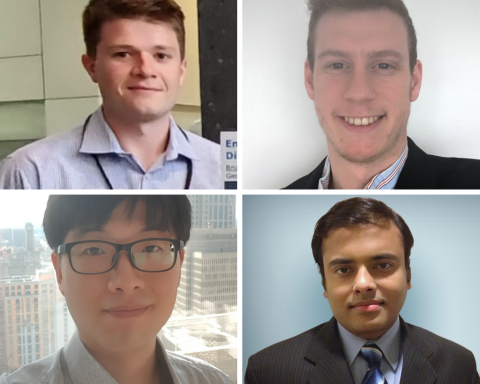

Brian Crafton, Samuel Spetalnick, Jong-Hyeok Yoon, and Arijit Raychowdhury won the Best Paper Award at this year's ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED 2021).

Brian Crafton, Samuel Spetalnick, Jong-Hyeok Yoon, and Arijit Raychowdhury won the Best Paper Award at this year's ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED 2021). The symposium was held July 26-28 in a virtual format.

Crafton and Spetalnick are Ph.D. students in the Georgia Tech School of Electrical and Computer Engineering (ECE), where they are advised by Raychowdhury, who holds the Motorola Solutions Foundation Professorship. He also leads the Integrated Circuits and Systems Research Lab (ICSRL). Yoon was a postdoctoral researcher in ICSRL until December 2020, and he is now an assistant professor in the Department of Information and Communication Engineering at the Daegu Gyeongbuk Institute of Science and Technology in Daegu, South Korea.

The title of the team’s paper is “Statistical Optimization of Compute In-Memory Performance Under Device Variation.” Compute in-memory using emerging non-volatile memory technologies is an exciting technique that promises to increase memory throughput and perform compute on the bitline of memory sub-arrays, thus accelerating machine learning workloads. However, this technique faces new challenges not before faced in traditional CMOS memory fabrics. The impact of the inherent spatial and temporal variations in memory cells is exacerbated when several are read on the same bitline. These variations result in significantly higher bit error-rates. As a result, performance must be limited to mitigate the high error rate.

This work presents a novel technique to maximize the performance of compute in-memory while satisfying an error constraint. Error models are constructed based on measurements collected on a 40nm foundry array, and an optimization problem is formulated and solved using integer linear programming. Using this technique, an optimal tradeoff of performance and accuracy is met enabling significant speedup over prior work.

This research is funded by Air Force Office for Scientific Research through the CEREBRAL MURI program and by SRC through the JUMP programs.