ECE's Hyung Suk (James) Yang, Chaoqi Zhang, and Muhannad Bakir have been named the winners of the 2014 IEEE Transactions on Components, Packaging, and Manufacturing Technology Best Paper Award in the Advanced Packaging Technologies category.

Hyung Suk (James) Yang, Chaoqi Zhang, and Muhannad Bakir have been named the winners of the 2014 IEEE Transactions on Components, Packaging, and Manufacturing Technology Best Paper Award in the Advanced Packaging Technologies category. They will be presented with the award at the 65th IEEE Electronic Components and Technology Conference, which will be held May 26-29 in San Diego.

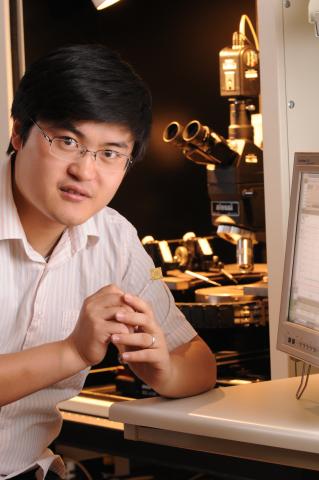

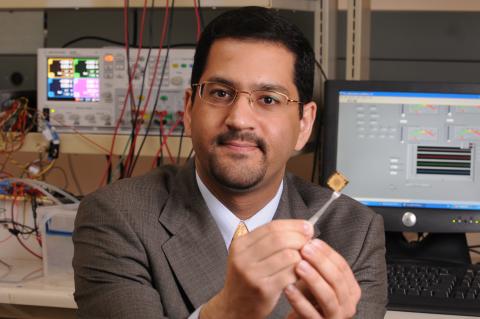

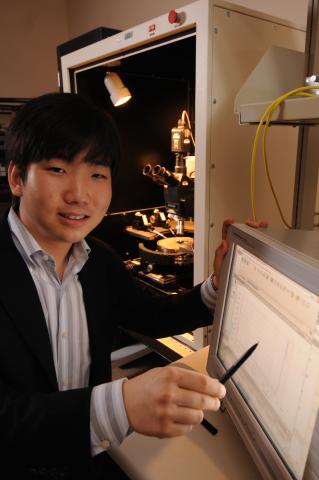

Yang and Zhang are Ph.D. students in the Georgia Tech School of Electrical and Computer Engineering (ECE). They are advised by Bakir, who is the ON Semiconductor Junior Professor in ECE and director of the Integrated 3D Systems (I3DS) Group.

The title of the team’s award-winning paper is “Self-Aligned Silicon Interposers, Tiles, and Silicon Bridges Using Positive Self-Alignment Structures and Rematable Mechanically Flexible Interconnects.” Silicon interposer-based interconnection has attracted significant research attention recently due to the growing need for larger bandwidth density and lower energy-per-bit off-chip communication. The key feature of silicon interposer-based systems is the use of legacy CMOS processes to form a dense array of fine-pitch electrical wires (and silicon photonics in some cases) on a silicon substrate to interconnect heterogeneous integrated circuits; in essence, future "advanced packaging" will highly leverage silicon CMOS based processes.

However, the interposer-based interconnection is only a partial solution to the rapidly growing chip-to-chip bandwidth requirement, because an interposer size is limited by both technical and economical constraints, and in turn, it ultimately limits the size and the number of chips that can be assembled on top. Eventually, multiple interposers may become necessary, and high-bandwidth interconnections between interposers will become vital in providing a high-performance large-scale system.

To this end, a large-scale contiguous all-silicon system platform has been proposed and demonstrated. In this paper, three silicon interposer tiles are aligned and mounted on a printed wiring board (PWB), and two silicon bridges are aligned and mounted on top of the three interposer tiles; each silicon bridge spans two interposer tiles. Four positive self-alignment structures and four inverted pyramid pits self-align a tile to the PWB and a bridge to two tiles. Mechanically flexible interconnects (MFI) form nonbonding electrical connections between the three interposer tiles and two silicon bridges. Pointy tips on the MFIs form low contact resistance with the pads on the silicon bridges. A small alignment error is demonstrated between the interposer tiles, which is critical for silicon photonic interconnection.

Additional Images